Разработан компьютерный чип с низким энергопотреблением

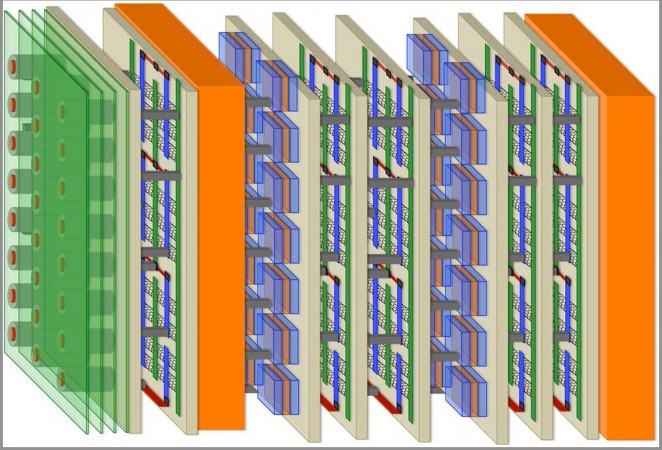

Группа исследователей из Стэнфордского университета разработала компьютерный чип с «многоэтажной» архитектурой, в которой процессорные слои чередуются со слоями памяти.

Новая разработка получила название N3XT (Nano-Engineered Computing Systems Technology, нано-инженерная технология вычислительных систем), пишет N+1. По данным разработчиков, такая архитектура позволит сделать новые чипы более производительными и менее энергопотребляющими.

В новом чипе процессоры и память соединены миллионами коротких электропроводящих дорожек, обеспечивающих обмен сигналами между всеми компонентами.

По словам профессора Филипа Вонга, участвующего в разработке, при сопоставимом с обычными чипами количестве вычислительных единиц и объема памяти новый многослойный чип будет превосходить по производительности старый в тысячу раз.

Современные процессорные чипы строятся по «одноэтажной» технологии. Все зоны чипа, расположенные в одной плоскости, электрически соединены друг с другом, однако множественные длинные электрические соединения несколько снижают общую производительность чипа и повышают энергопотребление.

Изображение: news.stanford.edu